VOL 2 ISSUE 2 (2016) PAGES 899-903

RECEIVED: 27/03/2016. PUBLISHED: 05/04/2016

April 5, 2016

# SIMULATION AND SHORT CHANNEL EFFECT ANALYSIS OF InAIN/GaN MOSHEMT WITH InGaN BACK BARRIER

M.Sathish kumar<sup>1</sup>, P.Sridharan<sup>2</sup>, P.Vinayagam<sup>3</sup>

PG Scholar VLSI Design, SKP Engineering College, Tiruvannamalai,

Asst Professor Dept of Electronics and communication, SKP Engineering College, Tiruvannamalai.

#### **Abstract:**

In this present work of InAlN/GaN high-electron mobility transistor (HEMT) with a three-terminal OFF-state breakdown voltage (BV) and a low specific on-resistance. To suppress the short-channel effects (SCEs), an InGaN back barrier is applied in an InAlN/GaN hetero structure. To reduce the drain-to-source leakage current in this device, an InGaN back barrier has been used. The gate leakage current in these devices is owing to use of a  $SiO_2$  layer. This current level is more than six orders of magnitude lower than in Schottky-barrier HEMT. The combination of InGaN back barrier, the high charge sheet density of InAlN/GaN HEMTs, and the low leakage because of the gate-dielectric layer allows for a figure-of-merit BV/RON,SP. In a gate-length device with on-resistance and an extrinsic transconductance, a peak  $f_T$  is achieved. An electron velocity was extracted by two different delay analysis methods.

**Keywords-** Back barrier, current gain cutoff frequency( $f_T$ ), GaN, metal oxide semiconductor highelectron-mobility transistor (HEMT), InAlN,InGaN, short-channel effect (SCE),Break down voltage.

#### 1. INTRODUCTION

The combination of high electron mobility and large breakdown voltage make GaN an ideal candidate to high-speed and high-power application. AlGaN/GaN high electron-mobility transistor (HEMT) with sio<sub>2</sub> gate oxide layer have traditionally led this field, and they have demonstrated an outstanding radiofrequency(R<sub>F</sub>) performance with 225 GHz current gain cutoff frequency and 300 GHz power gain cutoff frequency  $(f_{\text{max}})$ . However, device scaling below 50-nm gate length  $(L_p)$  is very challenging in AlGaN/GaN heterostructures because of difficulty in maintaining a sufficiently high aspect ratio (Lg/d, where d is the barrier thickness) to suppress short-channel effects (SCEs). Gate recess etching is used to improve aspect ratio; however, the dry etching process required the gate recess can induce damage in the channel as well as non uniformities across the wafer. In general, the breakdown voltage (BV) in HEMT devices scales with gate-to-drain distance ( $L_{gd}$ ). However, increasing  $L_{gd}$  also increases the drain series resistance, which degrades the output power efficiency. To minimize the on-resistance, it is therefore desirable to select heterostructures with a high sheet charge density, although this can reduce the BV of the device. The InAlN/GaN HEMT is a promising high-power switching device with a potential for very low specific on-resistance carrier. In this letter, a 3.3-nm In<sub>0.15</sub>Ga<sub>0.85</sub>N back barrier is used, instead of an AlGaN buffer, to increase the carrier confinement in InAlN/GaN HEMTs on SiC. The dc and RF performances of devices with gate length varying from 30 to 230 nm are investigated. In the 30-nm-gatelength device with an on resistance of 1.2  $\Omega$  · mm and an extrinsic transconductance of 530 mS/mm, an  $f_T$  of 300 GHz was achieved. This is the highest  $f_T$  reported so far in GaN-based transistors. An electron velocity in the  $1.37-1.45 \times 10^7$  cm/s range was extracted in this device by two different methods.

VOL 2 ISSUE 2 (2016) PAGES 899-903

RECEIVED: 27/03/2016. PUBLISHED: 05/04/2016

April 5, 2016

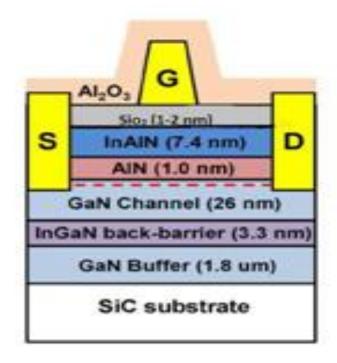

#### 2. DEVICE FABRICATION

A simplified cross-sectional view of the fabricated InAlN/GaN MOSHEMTs with an InGaN back barrier is shown in Fig. 1. The lattice matched In<sub>0.17</sub>Al  $_{0.83}$ N/GaN 3000-V 4.3-m $\Omega$  · cm² InAlN/GaN MOSHEMT with InGaN back barrier heterostructure is grown by metal—organic chemical vapor deposition on a semi-insulating SiC substrate[6]. After an AlN nucleation layer, a 0.85- $\mu$ m 4% InGaN back barrier is deposited, followed by a 26-nm-thick GaN channel.. Then, ohmic contacts are formed with a metal stack deposition and subsequent annealing at 820 °C for 60 s. A contact resistance of 0.3–0.4  $\Omega$  · mm is obtained. The source-to-drain distance is 1  $\mu$ m. After the ohmic contact fabrication, an oxygen plasma is applied everywhere on the wafer for reduce the gate leakage current and to improve RF performance. This sio<sub>2</sub> forms a 1–2-nm oxide layer on top of the InAlN layer. Sub micrometer gates with lengths from 30 to 230 nm were defined in the middle of the source—drain region by electron-beam lithography. To study the impact of the InGaN back barrier, samples with a GaN buffer and no back barrier were also grown as control and the AlN

Fig.2.Device Fabrication

The thin AlN interlayer between the  $In_{0.17}Al_{0.83}N$  layer and the GaN channel help to reduce interface roughness and improve two dimensional electron gas electron gas(2DEG) mobility. A total of  $1.5 \times 1013$  cm<sup>-2</sup> 2DEG charge density cm<sup>-2</sup>, an electron mobility of 1389 cm<sup>2</sup>/V · s, and a sheet resistance of 290  $\Omega$ /\_ are measured by the Hall technique at room temperature[2]. The device fabrication is started with mesa isolation, performed by electron-cyclotron-resonance etching with a plasma gas mixture. A 5 metal stack was evaporated on both source and drain regions after surface cleaning. The sample is then annealed in 850 °C for 30 s to form ohmic contacts.

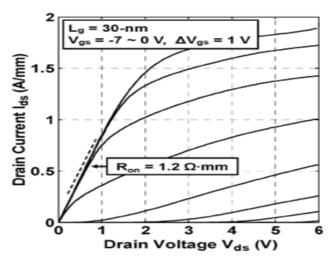

Fig.2.  $I_{ds}$  versus  $V_{ds}$  characteristics of the device with  $L_g = 30$  nm

A contact resistance of  $0.7~\Omega$  · mm is measured by a transmission-line-method structure. After the cleaning and UV ozone treatment, a 13.5-nm thick  $sio_2was$  deposited by atomic layer deposition at 250~°C gate dielectric. Finally, a gate electrode was deposited in a high vacuum electron-beam evaporator. A reference Schottky barrier HEMT sample was prepared without a  $SiO_2$  gate-dielectric layer to compare with the MOSHEMT devices. Finally, a gate electrode was deposited in a high vacuum electron-beam evaporator. A reference Schottky barrier HEMT sample was prepared without a  $SiO_2$  gate-dielectric layer to compare with the MOSHEMT devices. The devices have a gate length  $L_g = 2~\mu m$ , gate width  $W_g = 100~\mu m$ , gate-to-source distance  $L_{gs} = 1.5~\mu m$ , and a gate-to-drain distance  $L_{gd}$  varied from 2 to 30  $\mu m$ .

#### 3. RESULTS AND DSCUSSION

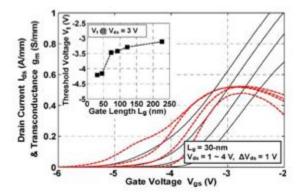

The dc performance of the fabricated devices is characterized with a agilent 4155 parameter analyzer. In spite of the thick top barrier (9.4–10.4 nm), the combination of the back barrier and the thin GaN channel allow an effective suppression of the SCE down to 70-nm gate lengths; a small threshold of about 0.3 V was observed when the gate length was reduced from 250 down to 70 nm. However, as the gate length is scaled below 50 nm, the SCEs become evident, and the  $V_T$  decreases rapidly ( $\Delta VT \approx 0.7$  V).

Fig.3. corresponding transfer curve at  $V_{\rm ds} = 1-4$

April 5, 2016

Fig. 3 shows the dc output and transfer characteristics of the InAlN/GaN MOSHEMTs with 30-nm gate length .At  $V_{\rm gs} = 0$  V, the device show a drain current over 1.8 A/mm with an on-resistance of 1.2  $\Omega$  · mm.

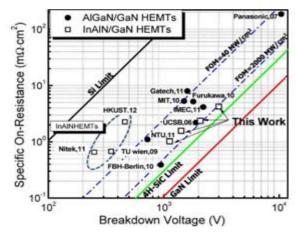

Fig.4. Specific on-resistance and BV of AlGaN/GaN and InAlN/GaN HEMTs

The peak extrinsic trans conductance of 520–530 mS/mm was obtained at  $V_{\rm ds} = 2-4$  V, and a threshold voltage  $(V_T)$  of -4.2 V is extracted at  $V_{\rm ds} = 3$  V. The  $f_T/f_{\rm max}$  value before de-embedding are 200/34 GHz, respectively. As shown in the inset in Fig. 4, the  $f_T \times Lg$  product decrease as the gate length scale down (17.3 GHz  $\cdot$   $\mu$ m for Lg = 230 nm and 9.0 GHz  $\mu$ m for Lg = 30 nm). This decreases is mainly due to the total delay dominated by extrinsic and parasitic components. To extract the electron velocity to the device accurately, two different method are used. First, based on the delay analysis by Moll et al. [15], the parasitic charging delay was extracted at the effective bias condition [= Vds - Ids  $\cdot$  ( $R_s + R_d$ )]. An electron velocity 1.37  $\times$  107 cm/s is obtained from the slope of the plot of "total delay–parasitic charging delay" versus "gate length ( $L_g$ )," as shown in Fig. 6. As a second approach, the intrinsic gate capacitance (Cgs.int and Cgd.int) and gm.int were extracted from the small-signal S-parameter at the same bias condition used in the first method, and an electron velocity of 1.45  $\times$  107 cm/s was calculated from the slope of the intrinsic delay.

### **CONCLUSION**

We have studied by the simulation of InAln/GaN with InGaN back barrier (for mole concentration x=0.17) using MOSHEMT, where the effect of - InGaN back barrier layer on the device performance of the proposed structure of InAln/GaN Gate-Recessed Enhancement-Mode MOSHEMT. These results obtained from the simulations are compared with the previously reported results by other group of the device without back barrier layer. These device with InGaN back barrier shows the excellent electrostatic control leading to obtain a very low gate leakage value. These device also shows a very high electron velocity of 1.37– $1.45 \times 10^7$  cm/s.

#### **REFERENCES**

[1] Chung. J.W., Kim .T.-W, and Palacios. T(2010)., "Advanced gate technologies for state-of-the-art  $f_T$  in AlGaN/GaN HEMTs," in *IEDM Tech. Dig.*, ,pp. 676–679, Paper 30.2.

## INTERNATIONAL RESEARCH JOURNAL IN ADVANCED ENGINEERING AND TECHNOLOGY (IRJAET) E - ISSN: 2454-4752 P - ISSN: 2454-4744

VOL 2 ISSUE 2 (2016) PAGES 899-903

RECEIVED: 27/03/2016. PUBLISHED: 05/04/2016

April 5, 2016

- [2] Chung J. W, Hoke W. E, Chumbes E. M, and Palacios T, "AlGaN/GaN HEMT with 300-GHz f<sub>max</sub>," *IEEE Electron Device Lett.*, vol. 31, no. 3,pp. 195–197, Mar. 2010.

- [3] Gao. X, Gorka. D, Pan. M, Oliver. M., Guo. S,. Lee. D. S, Palacios. T., Saunier. P, and Ketterson. A,(2011) "Ultra-thin InAlN HEMTs grown with back-barriers," presented at the 9th Int. Conf. Nitride Semiconductors, Glasgow, U.K., Jul., PB2.05.

- [4] Higashiwaki. M, Mimura. T., and Matsui. T,(2008) "AlGaN/GaN heterostructure field-effect transistors on 4H–SiC substrates with current-gain cutoff frequency of 190 GHz," *Appl. Phys. Exp.*, vol. 1, no. 2, pp. 021103-1–021103-3,

- [5] Kuzmik. J,(2001) "Power electronics on InAlN/(In)GaN: Prospect for a record performance," *IEEE Electron Device Lett.*, vol. 22, no. 11, pp. 510–512,.

- Lee. D. S, Chung. J. W, Wang. H, Gao. X, Guo. S, Fay. P, and Palacios. T,(2011)"245-GHz InAlN/GaN HEMTs with oxygen plasma treatment," *IEEE Electron Device Lett.*, vol. 32, no. 6, pp. 755–757, Jun.

- [7] Liu. J, Zhou. Y, Zhu. J, Lau .K. M., and Chen. K. J.(2006.), "AlGaN/GaN/ InGaN/GaN DH-HEMTs with an InGaN notch for enhanced carrier confinement," *IEEE Electron Device Lett.*, vol. 27, no. 1, pp. 10–12,

- [8] Lee. D. S, Gao. X., Guo .S, and Palacios. T(2011), "InAlN/GaN HEMTs with AlGaN back barriers," *IEEE Electron Device Lett.*, vol. 32, no. 5, pp. 617–619,.